ARM Cortex-M

The ARM Cortex-M is a group of 32-bit RISC ARM processor cores licensed by Arm Holdings. These cores are optimized for low-cost and energy-efficient microcontrollers, which have been embedded in tens of billions of consumer devices.[1] The cores consist of the Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33, Cortex-M35P, Cortex-M55.[2][3][4][5][6][7][8] The Cortex-M4 / M7 / M33 / M35P / M55 cores have an FPU silicon option, and when included in the silicon these cores are sometimes known as "Cortex-Mx with FPU" or "Cortex-MxF", where 'x' is the core number.

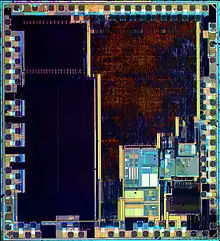

24 MHz ARM Cortex-M3 microcontroller with 16 KB flash memory, 4 KB RAM. Manufactured by STMicroelectronics.

Overview

| 32-bit | |

|---|---|

| Year | Core |

| 2004 | Cortex-M3 |

| 2007 | Cortex-M1 |

| 2009 | Cortex-M0 |

| 2010 | Cortex-M4 |

| 2012 | Cortex-M0+ |

| 2014 | Cortex-M7 |

| 2016 | Cortex-M23 |

| 2016 | Cortex-M33 |

| 2018 | Cortex-M35P |

| 2020 | Cortex-M55 |

The ARM Cortex-M family are ARM microprocessor cores which are designed for use in microcontrollers, ASICs, ASSPs, FPGAs, and SoCs. Cortex-M cores are commonly used as dedicated microcontroller chips, but also are "hidden" inside of SoC chips as power management controllers, I/O controllers, system controllers, touch screen controllers, smart battery controllers, and sensors controllers.

Though 8-bit microcontrollers were very popular in the past, Cortex-M has slowly been chipping away at the 8-bit market as the prices of low-end Cortex-M chips have moved downward. Cortex-M have become a popular replacements for 8-bit chips in applications that benefit from 32-bit math operations, and replacing older legacy ARM cores such as ARM7 and ARM9.

License

Arm Holdings neither manufactures nor sells CPU devices based on its own designs, but rather licenses the processor architecture to interested parties. Arm offers a variety of licensing terms, varying in cost and deliverables. To all licensees, Arm provides an integratable hardware description of the ARM core, as well as complete software development toolset and the right to sell manufactured silicon containing the ARM CPU.

Silicon customization

Integrated Device Manufacturers (IDM) receive the ARM Processor IP as synthesizable RTL (written in Verilog). In this form, they have the ability to perform architectural level optimizations and extensions. This allows the manufacturer to achieve custom design goals, such as higher clock speed, very low power consumption, instruction set extensions (including floating point), optimizations for size, debug support, etc. To determine which components have been included in a particular ARM CPU chip, consult the manufacturer datasheet and related documentation.

Some of the silicon options for the Cortex-M cores are:

- SysTick timer: A 24-bit system timer that extends the functionality of both the processor and the Nested Vectored Interrupt Controller (NVIC). When present, it also provides an additional configurable priority SysTick interrupt.[9][10][11] Though the SysTick timer is optional, it is very rare to find a Cortex-M microcontroller without it. If a Cortex-M33 microcontroller has the Security Extension option, then it has two SysTicks, one Secure and one Non-secure.

- Bit-Band: Maps a complete word of memory onto a single bit in the bit-band region. For example, writing to an alias word will set or clear the corresponding bit in the bit-band region. This allows every individual bit in the bit-band region to be directly accessible from a word-aligned address. In particular, individual bits can be set, cleared, or toggled from C/C++ without performing a read-modify-write sequence of instructions.[9][10][11] Though the bit-band is optional, it is less common to find a Cortex-M3 and Cortex-M4 microcontroller without it. Some Cortex-M0 and Cortex-M0+ microcontrollers have bit-band.

- Memory Protection Unit (MPU): Provides support for protecting regions of memory through enforcing privilege and access rules. It supports up to eight different regions, each of which can be split into a further eight equal-size sub-regions.[9][10][11]

- Tightly-Coupled Memory (TCM): Low-latency RAM that is used to hold critical routines, data, stacks. Other than cache, it is typically the fastest RAM in the microcontroller.

| ARM Core | Cortex M0[2] | Cortex M0+[3] | Cortex M1[4] | Cortex M3[5] | Cortex M4[6] | Cortex M7[7] | Cortex M23[8] | Cortex M33[12] | Cortex M35P |

|---|---|---|---|---|---|---|---|---|---|

| SysTick 24-bit Timer | Optional (0,1) | Optional (0,1) | Optional (0,1) | Yes (1) | Yes (1) | Yes (1) | Optional (0,1,2) | Yes (1,2) | Yes (1,2) |

| Single-cycle I/O port | No | Optional | No | No | No | No | Optional | No | No |

| Bit-Band memory | No[13] | No[13] | No* | Optional | Optional | Optional | No | No | No |

| Memory Protection Unit (MPU) | No | Optional (0,8) | No | Optional (0,8) | Optional (0,8) | Optional (0,8,16) | Optional (0,4,8,12,16) | Optional (0,4,8,12,16) | Optional * |

| Security Attribution Unit (SAU) and Stack Limits | No | No | No | No | No | No | Optional (0,4,8) | Optional (0,4,8) | Optional * |

| Instruction TCM | No | No | Optional | No | No | Optional | No | No | No |

| Data TCM | No | No | Optional | No | No | Optional | No | No | No |

| Instruction Cache | No[14] | No[14] | No[14] | No[14] | No[14] | Optional | No | No | Optional |

| Data Cache | No[14] | No[14] | No[14] | No[14] | No[14] | Optional | No | No | No |

| Vector Table Offset Register (VTOR) | No | Optional (0,1) | Optional (0,1) | Optional (0,1) | Optional (0,1) | Optional (0,1) | Optional (0,1,2) | Yes (1,2) | Yes (1,2) |

- Note: Most Cortex-M3 and M4 chips have bit-band and MPU. The bit-band option can be added to the M0/M0+ using the Cortex-M System Design Kit.[13]

- Note: Software should validate the existence of a feature before attempting to use it.[11]

- Note: Limited public information is available for the Cortex-M35P until its Technical Reference Manual is released.

Additional silicon options:[9][10]

- Data endianness: Little-endian or big-endian. Unlike legacy ARM cores, the Cortex-M is permanently fixed in silicon as one of these choices.

- Interrupts: 1 to 32 (M0/M0+/M1), 1 to 240 (M3/M4/M7/M23), 1 to 480 (M33/M35P).

- Wake-up interrupt controller: Optional.

- Vector Table Offset Register: Optional. (not available for M0).

- Instruction fetch width: 16-bit only, or mostly 32-bit.

- User/privilege support: Optional.

- Reset all registers: Optional.

- Single-cycle I/O port: Optional. (M0+/M23).

- Debug Access Port (DAP): None, SWD, JTAG and SWD. (optional for all Cortex-M cores)

- Halting debug support: Optional.

- Number of watchpoint comparators: 0 to 2 (M0/M0+/M1), 0 to 4 (M3/M4/M7/M23/M33/M35P).

- Number of breakpoint comparators: 0 to 4 (M0/M0+/M1/M23), 0 to 8 (M3/M4/M7/M33/M35P).

Instruction sets

The Cortex-M0 / M0+ / M1 implement the ARMv6-M architecture,[9] the Cortex-M3 implements the ARMv7-M architecture,[10] the Cortex-M4 / Cortex-M7 implements the ARMv7E-M architecture,[10] the Cortex-M23 / M33 / M35P implement the ARMv8-M architecture,[15] and the Cortex-M55 implements the ARMv8.1-M architecture.[16] The architectures are binary instruction upward compatible from ARMv6-M to ARMv7-M to ARMv7E-M. Binary instructions available for the Cortex-M0 / Cortex-M0+ / Cortex-M1 can execute without modification on the Cortex-M3 / Cortex-M4 / Cortex-M7. Binary instructions available for the Cortex-M3 can execute without modification on the Cortex-M4 / Cortex-M7 / Cortex-M33 / Cortex-M35P.[9][10] Only Thumb-1 and Thumb-2 instruction sets are supported in Cortex-M architectures; the legacy 32-bit ARM instruction set isn't supported.

All Cortex-M cores implement a common subset of instructions that consists of most Thumb-1, some Thumb-2, including a 32-bit result multiply. The Cortex-M0 / Cortex-M0+ / Cortex-M1 / Cortex-M23 were designed to create the smallest silicon die, thus having the fewest instructions of the Cortex-M family.

The Cortex-M0 / M0+ / M1 include Thumb-1 instructions, except new instructions (CBZ, CBNZ, IT) which were added in ARMv7-M architecture. The Cortex-M0 / M0+ / M1 include a minor subset of Thumb-2 instructions (BL, DMB, DSB, ISB, MRS, MSR). The Cortex-M3 / M4 / M7 / M33 / M35P have all base Thumb-1 and Thumb-2 instructions. The Cortex-M3 adds three Thumb-1 instructions, all Thumb-2 instructions, hardware integer divide, and saturation arithmetic instructions. The Cortex-M4 adds DSP instructions and an optional single-precision floating-point unit (VFPv4-SP). The Cortex-M7 adds an optional double-precision FPU (VFPv5).[9][10] The Cortex-M23 / M33 add TrustZone instructions.

| Arm Core | Cortex M0[2] | Cortex M0+[3] | Cortex M1[4] | Cortex M3[5] | Cortex M4[6] | Cortex M7[7] | Cortex M23[8] | Cortex M33[12] | Cortex M35P | Cortex M55 |

|---|---|---|---|---|---|---|---|---|---|---|

| ARM architecture | ARMv6-M[9] | ARMv6-M[9] | ARMv6-M[9] | ARMv7-M[10] | ARMv7E-M[10] | ARMv7E-M[10] | ARMv8-M Baseline[15] | ARMv8-M Mainline[15] | ARMv8-M Mainline[15] | Armv8.1-M |

| Computer architecture | Von Neumann | Von Neumann | Von Neumann | Harvard | Harvard | Harvard | Von Neumann | Harvard | Harvard | Harvard |

| Instruction pipeline | 3 stages | 2 stages | 3 stages | 3 stages | 3 stages | 6 stages | 2 stages | 3 stages | 3 stages | 4 to 5 stages |

| Thumb-1 instructions | Most | Most | Most | Entire | Entire | Entire | Most | Entire | Entire | Entire |

| Thumb-2 instructions | Some | Some | Some | Entire | Entire | Entire | Some | Entire | Entire | Entire |

| Multiply instructions 32x32 = 32-bit result | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Multiply instructions 32x32 = 64-bit result | No | No | No | Yes | Yes | Yes | No | Yes | Yes | Yes |

| Divide instructions 32/32 = 32-bit quotient | No | No | No | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Saturated instructions | No | No | No | Some | Yes | Yes | No | Yes | Yes | Yes |

| DSP instructions | No | No | No | No | Yes | Yes | No | Optional | Optional | Optional |

| Single-Precision (SP) Floating-point instructions | No | No | No | No | Optional | Optional | No | Optional | Optional | Optional |

| Double-Precision (DP) Floating-point instructions | No | No | No | No | No | Optional | No | No | No | Optional |

| Half-Precisions (HP) | No | No | No | No | No | No | No | No | No | Optional |

| TrustZone instructions | No | No | No | No | No | No | Optional | Optional | Optional | Optional |

| Co-processor instructions | No | No | No | No | No | No | No | Optional | Optional | Optional |

| Helium technology | No | No | No | No | No | No | No | No | No | Optional |

| Interrupt latency (if zero-wait state RAM) | 16 cycles | 15 cycles | 23 for NMI 26 for IRQ | 12 cycles | 12 cycles | 12 cycles | 15 no security ext 27 security ext | TBD | TBD | TBD |

- Note: The Cortex-M0 / M0+ / M1 doesn't include these 16-bit Thumb-1 instructions: CBZ, CBNZ, IT.[9][10]

- Note: The Cortex-M0 / M0+ / M1 only include these 32-bit Thumb-2 instructions: BL, DMB, DSB, ISB, MRS, MSR.[9][10]

- Note: The Cortex-M0 / M0+ / M1 / M23 only has 32-bit multiply instructions with a lower-32-bit result (32bit × 32bit = lower 32bit), where as the Cortex-M3 / M4 / M7 / M33 / M35P includes additional 32-bit multiply instructions with 64-bit results (32bit × 32bit = 64bit). The Cortex-M4 / M7 (optionally M33 / M35P) include DSP instructions for (16bit × 16bit = 32bit), (32bit × 16bit = upper 32bit), (32bit × 32bit = upper 32bit) multiplications.[9][10]

- Note: The number of cycles to complete multiply and divide instructions vary across ARM Cortex-M core designs. Some cores have a silicon option for the choice of fast speed or small size (slow speed), so cores have the option of using less silicon with the downside of higher cycle count. An interrupt occurring during the execution of a divide instruction or slow-iterative multiply instruction will cause the processor to abandon the instruction, then restart it after the interrupt returns.

- Multiply instructions "32-bit result" – Cortex-M0/M0+/M23 is 1 or 32 cycle silicon option, Cortex-M1 is 3 or 33 cycle silicon option, Cortex-M3/M4/M7/M33/M35P is 1 cycle.

- Multiply instructions "64-bit result" – Cortex-M3 is 3–5 cycles (depending on values), Cortex-M4/M7/M33/M35P is 1 cycle.

- Divide instructions – Cortex-M3/M4 is 2–12 cycles (depending on values), Cortex-M7 is 3–20 cycles (depending on values), Cortex-M23 is 17 or 34 cycle option, Cortex-M33 is 2–11 cycles (depending on values), Cortex-M35P is TBD.

- Note: The Cortex-M4 / M7 / M33 / M35P has a silicon option choice of no FPU or single-precision (SP) FPU, and the Cortex-M7 adds a third silicon option of supporting both single-precision (SP) and double-precision (DP). If the Cortex-M4 / M7 / M33 / M35P has a FPU, then it is known as the Cortex-M4F / Cortex-M7F / Cortex-M33F / Cortex-M35PF.[9][10]

- Note: The Cortex-M series includes three new 16-bit Thumb-1 instructions for sleep mode: SEV, WFE, WFI.

- Note: Interrupt latency cycle count assumes: 1) stack located in zero-wait state RAM, 2) another interrupt function not currently executing, 3) Security Extension option doesn't exist, because it adds additional cycles. The Cortex-M cores with a Harvard computer architecture have a shorter interrupt latency than Cortex-M cores with a Von Neumann computer architecture.

| Group | Instr bits | Instructions | Cortex M0,M0+,M1 | Cortex M3 | Cortex M4 | Cortex M7 | Cortex M23 | Cortex M33,M35P | Cortex M55 |

|---|---|---|---|---|---|---|---|---|---|

| Thumb-1 | 16 | ADC, ADD, ADR, AND, ASR, B, BIC, BKPT, BLX, BX, CMN, CMP, CPS, EOR, LDM, LDR, LDRB, LDRH, LDRSB, LDRSH, LSL, LSR, MOV, MUL, MVN, NOP, ORR, POP, PUSH, REV, REV16, REVSH, ROR, RSB, SBC, SEV, STM, STR, STRB, STRH, SUB, SVC, SXTB, SXTH, TST, UXTB, UXTH, WFE, WFI, YIELD | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-1 | 16 | CBNZ, CBZ | No | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-1 | 16 | IT | No | Yes | Yes | Yes | No | Yes | Yes |

| Thumb-2 | 32 | BL, DMB, DSB, ISB, MRS, MSR | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-2 | 32 | SDIV, UDIV | No | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-2 | 32 | ADC, ADD, ADR, AND, ASR, B, BFC, BFI, BIC, CDP, CLREX, CLZ, CMN, CMP, DBG, EOR, LDC, LDM, LDR, LDRB, LDRBT, LDRD, LDREX, LDREXB, LDREXH, LDRH, LDRHT, LDRSB, LDRSBT, LDRSH, LDRSHT, LDRT, LSL, LSR, MCR, MCRR, MLA, MLS, MOV, MOVT, MRC, MRRC, MUL, MVN, NOP, ORN, ORR, PLD, PLDW, PLI, POP, PUSH, RBIT, REV, REV16, REVSH, ROR, RRX, RSB, SBC, SBFX, SEV, SMLAL, SMULL, SSAT, STC, STM, STR, STRB, STRBT, STRD, STREX, STREXB, STREXH, STRH, STRHT, STRT, SUB, SXTB, SXTH, TBB, TBH, TEQ, TST, UBFX, UMLAL, UMULL, USAT, UXTB, UXTH, WFE, WFI, YIELD | No | Yes | Yes | Yes | No | Yes | Yes |

| DSP | 32 | PKH, QADD, QADD16, QADD8, QASX, QDADD, QDSUB, QSAX, QSUB, QSUB16, QSUB8, SADD16, SADD8, SASX, SEL, SHADD16, SHADD8, SHASX, SHSAX, SHSUB16, SHSUB8, SMLABB, SMLABT, SMLATB, SMLATT, SMLAD, SMLALBB, SMLALBT, SMLALTB, SMLALTT, SMLALD, SMLAWB, SMLAWT, SMLSD, SMLSLD, SMMLA, SMMLS, SMMUL, SMUAD, SMULBB, SMULBT, SMULTT, SMULTB, SMULWT, SMULWB, SMUSD, SSAT16, SSAX, SSUB16, SSUB8, SXTAB, SXTAB16, SXTAH, SXTB16, UADD16, UADD8, UASX, UHADD16, UHADD8, UHASX, UHSAX, UHSUB16, UHSUB8, UMAAL, UQADD16, UQADD8, UQASX, UQSAX, UQSUB16, UQSUB8, USAD8, USADA8, USAT16, USAX, USUB16, USUB8, UXTAB, UXTAB16, UXTAH, UXTB16 | No | No | Yes | Yes | No | Optional | Yes |

| SP Float | 32 | VABS, VADD, VCMP, VCMPE, VCVT, VCVTR, VDIV, VLDM, VLDR, VMLA, VMLS, VMOV, VMRS, VMSR, VMUL, VNEG, VNMLA, VNMLS, VNMUL, VPOP, VPUSH, VSQRT, VSTM, VSTR, VSUB | No | No | Optional | Optional | No | Optional | Optional |

| DP Float | 32 | VCVTA, VCVTM, VCVTN, VCVTP, VMAXNM, VMINNM, VRINTA, VRINTM, VRINTN, VRINTP, VRINTR, VRINTX, VRINTZ, VSEL | No | No | No | Optional | No | No | Optional |

| TrustZone | 16 | BLXNS, BXNS | No | No | No | No | Optional | Optional | Optional |

| TrustZone | 32 | SG, TT, TTT, TTA, TTAT | No | No | No | No | Optional | Optional | Optional |

| Co-processor | 16 | CDP, CDP2, MCR, MCR2, MCRR, MCRR2, MRC, MRC2, MRRC, MRRC2 | No | No | No | No | No | Optional | Optional |

- Note: The single-precision (SP) FPU instructions are valid in the Cortex-M4 / M7 / M33 / M35P only when the SP FPU option exists in the silicon.

- Note: The double-precision (DP) FPU instructions are valid in the Cortex-M7 only when the DP FPU option exists in the silicon.

Deprecations

The ARM architecture for ARM Cortex-M series removed some features from older legacy cores:[9][10]

- The 32-bit ARM instruction set is not included in Cortex-M cores.

- Endianness is chosen at silicon implementation in Cortex-M cores. Legacy cores allowed "on-the-fly" changing of the data endian mode.

- Co-processor were not supported on Cortex-M cores, until the silicon option was reintroduced in "ARMv8-M Mainline" for ARM Cortex-M33/M35P cores.

The capabilities of the 32-bit ARM instruction set is duplicated in many ways by the Thumb-1 and Thumb-2 instruction sets, but some ARM features don't have a similar feature:

- The SWP and SWPB (swap) ARM instructions don't have a similar feature in Cortex-M.

The 16-bit Thumb-1 instruction set has evolved over time since it was first released in the legacy ARM7T cores with the ARMv4T architecture. New Thumb-1 instructions were added as each legacy ARMv5 / ARMv6 / ARMv6T2 architectures were released. Some 16-bit Thumb-1 instructions were removed from the Cortex-M cores:

- The "BLX <immediate>" instruction doesn't exist because it was used to switch from Thumb-1 to ARM instruction set. The "BLX <register>" instruction is still available in the Cortex-M.

- SETEND doesn't exist because on-the-fly switching of data endian mode is no longer supported.

- Co-processor instructions were not supported on Cortex-M cores, until the silicon option was reintroduced in "ARMv8-M Mainline" for ARM Cortex-M33/M35P cores.

- The SWI instruction was renamed to SVC, though the instruction binary coding is the same. However, the SVC handler code is different from the SWI handler code, because of changes to the exception models.

Cortex-M0

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv6-M |

| Instruction set | Thumb-1 (most), Thumb-2 (some) |

The Cortex-M0 core is optimized for small silicon die size and use in the lowest price chips.

Key features of the Cortex-M0 core are:[2]

- ARMv6-M architecture[9]

- 3-stage pipeline

- Instruction sets:

- Thumb-1 (most), missing CBZ, CBNZ, IT

- Thumb-2 (some), only BL, DMB, DSB, ISB, MRS, MSR

- 32-bit hardware integer multiply with 32-bit result

- 1 to 32 interrupts, plus NMI

Silicon options:

- Hardware integer multiply speed: 1 or 32 cycles.

Chips

The following microcontrollers are based on the Cortex-M0 core:

- ABOV AC30M1x64

- Cypress PSoC 4000, 4100, 4100M, 4200, 4200DS, 4200L, 4200M

- Infineon XMC1100, XMC1200, XMC1300, XMC1400, TLE984x

- Dialog DA1458x, DA1468x

- Nordic nRF51

- NXP LPC1100, LPC1200

- Nuvoton NuMicro

- Sonix SN32F700

- ST STM32 F0

- Toshiba TX00

- Vorago VA10800 (extreme temperature), VA10820 (radiation hardened)

The following chips have a Cortex-M0 as a secondary core:

- NXP LPC4300 (one Cortex-M4F + one Cortex-M0)

- Texas Instruments SimpleLink Wireless MCUs CC1310 and CC2650 (one programmable Cortex-M3 + one Cortex-M0 network processor + one proprietary Sensor Controller Engine)

Cortex-M0+

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv6-M |

| Instruction set | Thumb-1 (most), Thumb-2 (some) |

The Cortex-M0+ is an optimized superset of the Cortex-M0. The Cortex-M0+ has complete instruction set compatibility with the Cortex-M0 thus allowing the use of the same compiler and debug tools. The Cortex-M0+ pipeline was reduced from 3 to 2 stages, which lowers the power usage. In addition to debug features in the existing Cortex-M0, a silicon option can be added to the Cortex-M0+ called the Micro Trace Buffer (MTB) which provides a simple instruction trace buffer. The Cortex-M0+ also received Cortex-M3 and Cortex-M4 features, which can be added as silicon options, such as the memory protection unit (MPU) and the vector table relocation.[3]

Key features of the Cortex-M0+ core are:[3]

- ARMv6-M architecture[9]

- 2-stage pipeline (one fewer than Cortex-M0)

- Instruction sets: (same as Cortex-M0)

- Thumb-1 (most), missing CBZ, CBNZ, IT

- Thumb-2 (some), only BL, DMB, DSB, ISB, MRS, MSR

- 32-bit hardware integer multiply with 32-bit result

- 1 to 32 interrupts, plus NMI

Silicon options:

- Hardware integer multiply speed: 1 or 32 cycles

- 8-region memory protection unit (MPU) (same as M3 and M4)

- Vector table relocation (same as M3, M4)

- Single-cycle I/O port (available in M0+/M23)

- Micro Trace Buffer (MTB) (available in M0+/M23/M33/M35P)

Chips

The following microcontrollers are based on the Cortex-M0+ core:

- ABOV Semiconductor A31G11x, A31G12x, A31G314

- Cypress PSoC 4000S, 4100S, 4100S+, 4100PS, 4700S, FM0+

- Epson S1C31W74, S1C31D01, S1C31D50

- Holtek HT32F52000

- Microchip (Atmel) SAM C2, D0, D1, D2, DA, L2, R2, R3

- NXP LPC800, LPC11E60, LPC11U60

- NXP (Freescale) Kinetis E, EA, L, M, V1, W0

- Raspberry Pi RP2040 (two M0+ cores)

- Renesas S124, S128, RE, RE01

- Silicon Labs (Energy Micro) EFM32 Zero, Happy

- ST STM32 L0, G0

The following chips have a Cortex-M0+ as a secondary core:

The smallest ARM microcontrollers are of the Cortex-M0+ type (as of 2014, smallest at 1.6 mm by 2 mm is Kinetis KL03).[17]

On 21 June 2018, the "world's smallest computer'", or computer device was announced – based on the ARM Cortex-M0+ (and including RAM and wireless transmitters and receivers based on photovoltaics) – by University of Michigan researchers at the 2018 Symposia on VLSI Technology and Circuits with the paper "A 0.04mm3 16nW Wireless and Batteryless Sensor System with Integrated Cortex-M0+ Processor and Optical Communication for Cellular Temperature Measurement." The device is 1/10th the size of IBM's previously claimed world-record-sized computer from months back in March 2018, which is smaller than a grain of salt.

Cortex-M1

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv6-M |

| Instruction set | Thumb-1 (most), Thumb-2 (some) |

The Cortex-M1 is an optimized core especially designed to be loaded into FPGA chips.

Key features of the Cortex-M1 core are:[4]

- ARMv6-M architecture[9]

- 3-stage pipeline.

- Instruction sets:

- Thumb-1 (most), missing CBZ, CBNZ, IT.

- Thumb-2 (some), only BL, DMB, DSB, ISB, MRS, MSR.

- 32-bit hardware integer multiply with 32-bit result.

- 1 to 32 interrupts, plus NMI.

Silicon options:

- Hardware integer multiply speed: 3 or 33 cycles.

- Optional Tightly-Coupled Memory (TCM): 0 to 1 MB instruction-TCM, 0 to 1 MB data-TCM, each with optional ECC.

- External interrupts: 0, 1, 8, 16, 32.

- Debug: none, reduced, full.

- Data endianness: little-endian or BE-8 big-endian.

- OS extension: present or absent.

Cortex-M3

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv7-M |

| Instruction set | Thumb-1, Thumb-2, Saturated (some), Divide |

_MCU.jpg.webp)

Key features of the Cortex-M3 core are:[5][20]

- ARMv7-M architecture[10]

- 3-stage pipeline with branch speculation.

- Instruction sets:

- Thumb-1 (entire).

- Thumb-2 (entire).

- 32-bit hardware integer multiply with 32-bit or 64-bit result, signed or unsigned, add or subtract after the multiply. 32-bit multiply is 1 cycle, but 64-bit multiply and MAC instructions require extra cycles.

- 32-bit hardware integer divide (2–12 cycles).

- saturation arithmetic support.

- 1 to 240 interrupts, plus NMI.

- 12 cycle interrupt latency.

- Integrated sleep modes.

Silicon options:

- Optional Memory Protection Unit (MPU): 0 or 8 regions.

Chips

The following microcontrollers are based on the Cortex-M3 core:

- ABOV AC33Mx128, AC33Mx064

- Actel SmartFusion, SmartFusion 2

- Analog Devices ADUCM360, ADUCM361, ADUCM3029

- Broadcom Wi-Fi Chip BCM4319XKUBG

- Cypress PSoC 5000, 5000LP, FM3

- Holtek HT32F

- Infineon TLE9860, TLE987x

- Microchip (Atmel) SAM 3A, 3N, 3S, 3U, 3X

- NXP LPC1300, LPC1700, LPC1800

- ON Semiconductor Q32M210

- Realtek RTL8710

- Silicon Labs Precision32

- Silicon Labs (Energy Micro) EFM32 Tiny, Gecko, Leopard, Giant

- ST STM32 F1, F2, L1, W

- TDK-Micronas HVC4223F

- Texas Instruments F28, LM3, TMS470, OMAP 4, SimpleLink Wireless MCUs (CC1310 Sub-GHz and CC2650 BLE+ZigBee+6LoWPAN)

- Toshiba TX03

The following chips have a Cortex-M3 as a secondary core:

- Apple A9 (Cortex-M3 as integrated M9 motion co-processor)

- CSR Quatro 5300 (Cortex-M3 as co-processor)

- Samsung Exynos 7420 (Cortex-M3 as a DVS microcontroller)[21]

- Texas Instruments F28, LM3, TMS470, OMAP 4470 (one Cortex-A9 + two Cortex-M3)

- XMOS XS1-XA (seven xCORE + one Cortex-M3)

The following FPGAs include a Cortex-M3 core:

- Microsemi SmartFusion2 SoC

The following vendors support the Cortex-M3 as soft-cores on their FPGA chips:

Cortex-M4

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv7E-M |

| Instruction set | Thumb-1, Thumb-2, Saturated, DSP, Divide, FPU (SP) |

_MCU.JPG.webp)

_MCU.JPG.webp)

Conceptually the Cortex-M4 is a Cortex-M3 plus DSP instructions, and optional floating-point unit (FPU). A core with an FPU is known as Cortex-M4F.

Key features of the Cortex-M4 core are:[6]

- ARMv7E-M architecture[10]

- 3-stage pipeline with branch speculation.

- Instruction sets:

- Thumb-1 (entire).

- Thumb-2 (entire).

- 32-bit hardware integer multiply with 32-bit or 64-bit result, signed or unsigned, add or subtract after the multiply. 32-bit Multiply and MAC are 1 cycle.

- 32-bit hardware integer divide (2–12 cycles).

- Saturation arithmetic support.

- DSP extension: Single cycle 16/32-bit MAC, single cycle dual 16-bit MAC, 8/16-bit SIMD arithmetic.

- 1 to 240 interrupts, plus NMI.

- 12 cycle interrupt latency.

- Integrated sleep modes.

Silicon options:

- Optional floating-point unit (FPU): single-precision only IEEE-754 compliant. It is called the FPv4-SP extension.

- Optional memory protection unit (MPU): 0 or 8 regions.

Chips

The following microcontrollers are based on the Cortex-M4 core:

- Analog Devices ADSP-CM40x

- Microchip (Atmel) SAM 4L, 4N, 4S

- NXP (Freescale) Kinetis K, W2

- Texas Instruments SimpleLink Wi-Fi CC32xx, CC32xxMOD

The following microcontrollers are based on the Cortex-M4F (M4 + FPU) core:

- Analog Devices ADUCM4050

- Cypress 6200 (one Cortex-M4F + one Cortex-M0+), FM4

- Infineon XMC4000

- Maxim Darwin

- Microchip (Atmel) SAM4C (Dual core: one Cortex-M4F + one Cortex-M4), SAM4E, SAMG5, SAMD5/E5x

- Nordic nRF52

- Nuvoton NuMicro M480

- NXP LPC4000, LPC4300 (one Cortex-M4F + one Cortex-M0)

- NXP (Freescale) Kinetis K, V3, V4

- Renesas S3, S5, S7, RA4, RA6

- Silicon Labs (Energy Micro) EFM32 Wonder

- ST STM32 F3, F4, L4, L4+, WB (one Cortex-M4F + one Cortex-M0+)

- Texas Instruments LM4F, TM4C, MSP432, CC13x2R, CC1352P, CC26x2R

- Toshiba TX04

The following chips have either a Cortex-M4 or M4F as a secondary core:

- NXP (Freescale) Vybrid VF6 (one Cortex-A5 + one Cortex-M4F)

- NXP (Freescale) i.MX 6 SoloX (one Cortex-A9 + one Cortex-M4F)

- NXP (Freescale) i.MX 7 Solo/Dual (one or two Cortex-A7 + one Cortex-M4F)

- NXP (Freescale) i.MX 8 (two Cortex-A72 + four Cortex-A53 + two Cortex-M4F)

- NXP (Freescale) i.MX 8M and 8M Mini (four Cortex-A53 + one Cortex-M4F)

- NXP (Freescale) i.MX 8X (four Cortex-A35 + one Cortex-M4F)

- ST STM32MP1 (one or two Cortex-A7 + one Cortex-M4)

- Texas Instruments OMAP 5 (two Cortex-A15s + two Cortex-M4)

- Texas Instruments Sitara AM5700 (one or two Cortex-A15s + two Cortex-M4s as image processing units + two Cortex-M4s as general purpose units)

Cortex-M7

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv7E-M |

| Instruction set | Thumb-1, Thumb-2, Saturated, DSP, Divide, FPU (SP & DP) |

The Cortex-M7 is a high-performance core with almost double the power efficiency of the older Cortex-M4. It features a 6-stage superscalar pipeline with branch prediction and an optional floating-point unit capable of single-precision and optionally double-precision operations.[23][24] The instruction and data buses have been enlarged to 64-bit wide over the previous 32-bit buses. If a core contains an FPU, it is known as a Cortex-M7F, otherwise it is a Cortex-M7.

Key features of the Cortex-M7 core are:[7]

- ARMv7E-M architecture.

- 6-stage pipeline with branch speculation. Longest of all ARM Cortex-M cores.

- Instruction sets:

- Thumb-1 (entire).

- Thumb-2 (entire).

- 32-bit hardware integer multiply with 32-bit or 64-bit result, signed or unsigned, add or subtract after the multiply. 32-bit Multiply and MAC are 1 cycle.

- 32-bit hardware integer divide (2–12 cycles).

- Saturation arithmetic support.

- DSP extension: Single cycle 16/32-bit MAC, single cycle dual 16-bit MAC, 8/16-bit SIMD arithmetic.

- 1 to 240 interrupts, plus NMI.

- 12 cycle interrupt latency.

- Integrated sleep modes.

Silicon options:

- Optional floating-point unit (FPU): (single precision) or (single and double-precision), both IEEE-754-2008 compliant. It is called the FPv5 extension.

- Optional CPU cache: 0 to 64 KB instruction-cache, 0 to 64 KB data-cache, each with optional ECC.

- Optional Tightly-Coupled Memory (TCM): 0 to 16 MB instruction-TCM, 0 to 16 MB data-TCM, each with optional ECC.

- Optional Memory Protection Unit (MPU): 8 or 16 regions.

- Optional Embedded Trace Macrocell (ETM): instruction-only, or instruction and data.

- Optional Retention Mode (with Arm Power Management Kit) for Sleep Modes.

Cortex-M23

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv8-M Baseline |

| Instruction set | Thumb-1 (most), Thumb-2 (some), Divide, TrustZone |

The Cortex-M23 core was announced in October 2016[25] and based on the newer ARMv8-M architecture that was previously announced in November 2015.[26] Conceptually the Cortex-M23 is similar to a Cortex-M0+ plus integer divide instructions and TrustZone security features, and also has a 2-stage instruction pipeline.

Key features of the Cortex-M23 core are:[8][25]

- ARMv8-M Baseline architecture.[15]

- 2-stage pipeline. (similar to Cortex-M0+)

- TrustZone security instructions. (available only in M23/M33/M35P)

- 32-bit hardware integer divide (17 or 34 cycles). (not available in M0/M0+/M1) (slower than divide in all other cores)

- Stack limit boundaries. (available only with SAU option) (available in M23/M33/M35P)

Silicon options:

- Hardware integer multiply speed: 1 or 32 cycles.

- Hardware integer divide speed: 17 or 34 cycles maximum. Depending on divisor, instruction may complete in fewer cycles.

- Optional Memory Protection Unit (MPU): 0, 4, 8, 12, 16 regions.

- Optional Security Attribution Unit (SAU): 0, 4, 8 regions.

- Single-cycle I/O port (available in M0+/M23).

- Micro Trace Buffer (MTB) (available in M0+/M23/M33/M35P).

Cortex-M33

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv8-M Mainline |

| Instruction set | Thumb-1, Thumb-2, Saturated, DSP, Divide, FPU (SP), TrustZone, Co-processor |

The Cortex-M33 core was announced in October 2016[25] and based on the newer ARMv8-M architecture that was previously announced in November 2015.[26] Conceptually the Cortex-M33 is similar to a cross of Cortex-M4 and Cortex-M23, and also has a 3-stage instruction pipeline.

Key features of the Cortex-M33 core are:[12][25]

- ARMv8-M Mainline architecture.[15]

- 3-stage pipeline.

- TrustZone security instructions. (available only in M23/M33/M35P)

- 32-bit hardware integer divide (11 cycles maximum). (not available in M0/M0+/M1)

- Stack limit boundaries. (available only with SAU option) (available in M23/M33/M35P)

Silicon options:

- Optional Floating-Point Unit (FPU): single-precision only IEEE-754 compliant. It is called the FPv5 extension.

- Optional Memory Protection Unit (MPU): 0, 4, 8, 12, 16 regions.

- Optional Security Attribution Unit (SAU): 0, 4, 8 regions.

- Micro Trace Buffer (MTB) (available in M0+/M23/M33/M35P).

Chips

The following microcontrollers are based on the Cortex-M33 core:

- Analog Devices ADUCM410, ADUCM420

- Dialog DA1469x

- Nordic nRF91, nRF5340

- NXP LPC5500, i.MX RT600

- Renesas RA

- ST STM32 L5

- Silicon Labs Wireless Gecko Series 2

Cortex-M35P

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv8-M Mainline |

| Instruction set | Thumb-1, Thumb-2, Saturated, DSP, Divide, FPU (SP), TrustZone, Co-processor |

The Cortex-M35P core was announced in May 2018. It is conceptually a Cortex-M33 core with a new instruction cache, plus new tamper-resistant hardware concepts borrowed from the ARM SecurCore family, and configurable parity and ECC features.[27]

Limited public information is currently available for the Cortex-M35P until its Technical Reference Manual is released.

Chips

The following microcontrollers are based on the Cortex-M35P core:

- As of February 2020, no chips have been announced.

Cortex-M55

| Architecture and classification | |

|---|---|

| Microarchitecture | ARMv8.1-M Mainline Helium |

| Instruction set | Thumb-1, Thumb-2, Saturated, DSP, Divide, FPU (VFPv5), TrustZone, Coprocessor, MVE |

The Cortex-M55 core was announced in February 2020 and is based on the Armv8.1-M architecture that was previously announced in February 2019. It also has a 4-stage instruction pipeline.

Key features of the Cortex-M55 core include:

- ARMv8.1-M Mainline/Helium architecture.[15]

- 4-stage pipeline.

- Stack limit boundaries (available only with SAU option).

Silicon options:

- Helium (M-Profile Vector Extension, MVE)

- Single-Precision and Double-Precision floating-point

- Digital Signal Processing (DSP) extension support

- TrustZone security extension support

- Safety and reliability (RAS) support

- Coprocessor support

- Secure and Non-secure MPU with 0, 4, 8, 12, or 16 regions

- SAU with 0, 4, or 8 regions

- Instruction cache with size of 4KB, 8KB, 16KB, 32KB, 64KB

- Data cache with size of 4KB, 8KB, 16KB, 32KB, 64KB

- ECC on caches and TCMs

- 1–480 interrupts

- 3–8 exception priority bits

- Internal and external WIC options, optional CTI, ITM, and DWT

- ARM Custom Instructions (available in a future release)

Chips

The following microcontrollers are based on the Cortex-M55 core:

- As of February 2020, no chips have been announced.

Development tools

Documentation

The documentation for ARM chips is extensive. In the past, 8-bit microcontroller documentation would typically fit in a single document, but as microcontrollers have evolved, so has everything required to support them. A documentation package for ARM chips typically consists of a collection of documents from the IC manufacturer as well as the CPU core vendor (Arm Holdings).

A typical top-down documentation tree is:

- Documentation tree (top to bottom)

- IC manufacturer website.

- IC manufacturer marketing slides.

- IC manufacturer datasheet for the exact physical chip.

- IC manufacturer reference manual that describes common peripherals and aspects of a physical chip family.

- ARM core website.

- ARM core generic user guide.

- ARM core technical reference manual.

- ARM architecture reference manual.

IC manufacturers have additional documents, such as: evaluation board user manuals, application notes, getting started guides, software library documents, errata, and more. See External links section for links to official Arm documents.

See also

References

- ARM Cortex-M website; arm.com

- Cortex-M0 r0p0 Technical Reference Manual; Arm Holdings.

- Cortex-M0+ r0p0 Technical Reference Manual; Arm Holdings.

- Cortex-M1 r1p0 Technical Reference Manual; Arm Holdings.

- Cortex-M3 r2p1 Technical Reference Manual; Arm Holdings.

- Cortex-M4 r0p1 Technical Reference Manual; Arm Holdings.

- Cortex-M7 r0p2 Technical Reference Manual; Arm Holdings.

- Cortex-M23 r1p0 Technical Reference Manual; Arm Holdings.

- ARMv6-M Architecture Reference Manual; Arm Holdings.

- ARMv7-M Architecture Reference Manual; Arm Holdings.

- Cortex-M3 Embedded Software Development; App Note 179; Arm Holdings.

- Cortex-M33 r0p3 Technical Reference Manual; Arm Holdings.

- Cortex-M System Design Kit; Arm Holdings.

- ARM Cortex-M Programming Guide to Memory Barrier Instructions; Section 3.6 System implementation requirements; AppNote 321; arm.com

- ARMv8-M Architecture Reference Manual; Arm Holdings.

- ARMv8.1-M Architecture Reference Manual; Arm Holdings.

- Fingas, Jon (25 February 2014). "Freescale makes the world's smallest ARM controller chip even tinier". Retrieved 2 October 2014.

- GOWIN Semiconductor joins ARM DesignStart offering free ARM Cortex-M1 Processors for its FPGA product families

- Cortex-M1 DesignStart FPGA XilinxEdition

- Sadasivan, Shyam. "An Introduction to the ARM Cortex-M3 Processor" (PDF). Arm Holdings. Archived from the original (PDF) on July 26, 2014.

- "The Samsung Exynos 7420 Deep Dive - Inside a Modern 14nm SoC". AnandTech. Retrieved 2015-06-15.

- Cortex-M3 DesignStart FPGA XilinxEdition

- "Cortex-M7 Processor". Arm Holdings. Retrieved 2014-09-24.

- "ARM Supercharges MCU Market with High Performance Cortex-M7 Processor". arm.com (Press release). September 24, 2014.

- New ARM Cortex-M processors offer the next industry standard for secure IoT; Arm Holdings; October 25, 2016.

- ARMv8-M Architecture Simplifies Security for Smart Embedded Devices; Arm Holdings; November 10, 2015.

- "Cortex-M35P Processor". Arm Holdings. Retrieved 2018-06-04.

Further reading

- Embedded Systems with ARM Cortex-M Microcontrollers in Assembly Language and C; 3rd Ed; Yifeng Zhu; 738 pages; 2017; ISBN 978-0982692660.

- Designer's Guide to the Cortex-M Processor Family; 2nd Ed; Trevor Martin; 490 pages; 2016; ISBN 978-0081006290.

- ARM Assembly for Embedded Applications; 3rd Ed; Daniel Lewis; 318 pages; 2017; ISBN 978-1543908046.

- Definitive Guide to the ARM Cortex-M0 and Cortex-M0+ Processors; 2nd Ed; Joseph Yiu; 784 pages; 2015; ISBN 978-0128032770.

- Definitive Guide to the ARM Cortex-M3 and Cortex-M4 Processors; 3rd Ed; Joseph Yiu; 600 pages; 2013; ISBN 978-0124080829.

- Digital Signal Processing and Applications Using the ARM Cortex-M4; 1st Ed; Donald Reay; 250 pages; 2014; ISBN 978-1118859049.

- Embedded Systems: Introduction to ARM Cortex-M Microcontrollers; 5th Ed; Jonathan Valvano; 506 pages; 2012; ISBN 978-1477508992.

- Assembly Language Programming: ARM Cortex-M3; 1st Ed; Vincent Mahout; 256 pages; 2012; ISBN 978-1848213296.

External links

| Wikimedia Commons has media related to ARM Cortex-M. |

- ARM Cortex-M official documents

- ARM Cortex-M official website

- Cortex-M for Beginners – arm.com

- ARMv8-M Security Extensions – arm.com

- Cortex Microcontroller Software Interface Standard (CMSIS) – arm.com

ARM

coreBit

widthARM

websiteARM generic

user guideARM technical

reference manualARM architecture

reference manualCortex-M0 32 Link Link Link ARMv6-M Cortex-M0+ 32 Link Link Link ARMv6-M Cortex-M1 32 Link Link Link ARMv6-M Cortex-M3 32 Link Link Link ARMv7-M Cortex-M4 32 Link Link Link ARMv7E-M Cortex-M7 32 Link Link Link ARMv7E-M Cortex-M23 32 Link Link Link ARMv8-M Cortex-M33 32 Link Link Link ARMv8-M Cortex-M35P 32 Link TBD TBD ARMv8-M Cortex-M55 32 Link TBD TBD ARMv8.1-M

- Quick reference cards

- Instructions: Thumb-1 (1), ARM and Thumb-2 (2), Vector Floating-Point (3) – arm.com

- Opcodes: Thumb-1 (1, 2), ARM (3, 4), GNU Assembler Directives (5).

- Migrating

- Migrating from 8051 to Cortex-M3 – arm.com

- Migrating from PIC to Cortex-M3 – arm.com

- Migrating from ARM7TDMI to Cortex-M3 – arm.com

- Migrating from Cortex-M4 to Cortex-M7 – keil.com

- Other

.JPG.webp)